超能装!台积电第5代最新封装技能道路图发布

时间: 2024-02-21 08:56:31 | 作者: 安博体育

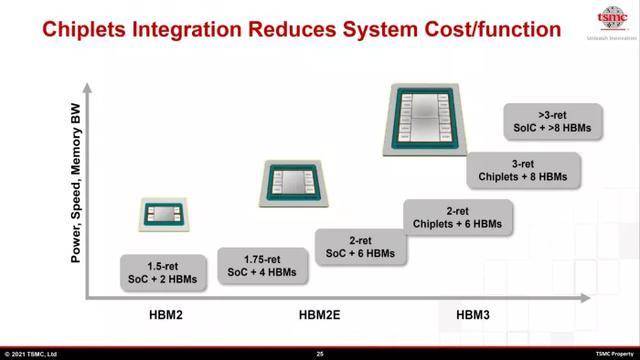

【新智元导读】近来,Hot Chip 33大会在线上举办,台积电在会上介绍了自家封装技能道路代CoWoS封装技能将于本年晚些时候面世,具有8个HBM2e仓库的空间,容量高达128 GB,比第3代技能多存储20倍晶体管,估计2023年发布第6代CoWoS。

第五代CoWoS封装技能将在本年晚些时候面世,与第三代封装技能比较,有望能够

到2019年8月,台积电CoWoS已经有60多种产品流片正在出产或开发中。

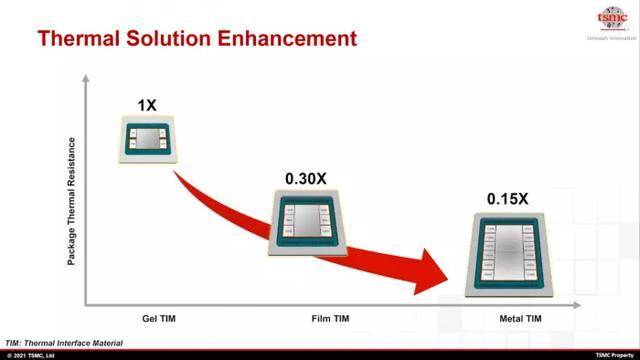

初代CoWoS封装技能是根据凝胶的热风化(Gel TIM),与之比较,台积电供给了最新的SOC散热解决方案。

现在关于第六代技能知之甚少,只能确认第六代技能将会在同一封装内包容多达8组HBM3内存和2组核算芯片。

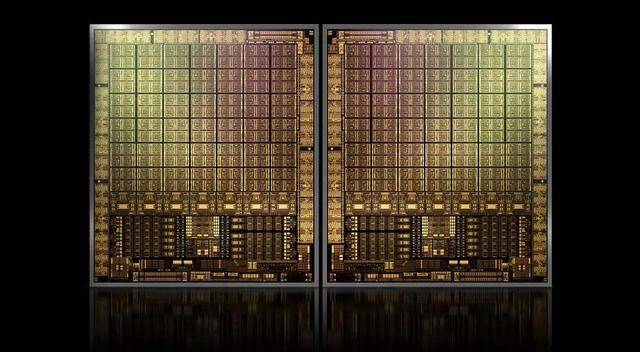

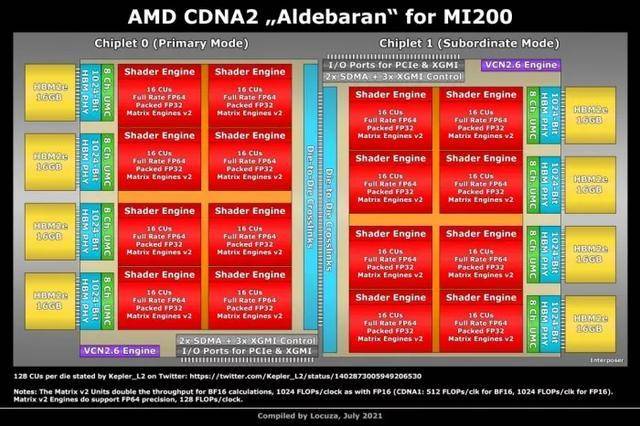

,超越16000个内核,能供给高达256个核算单元(CU)和128GB的HBM2E缓存。内部分为主、副两个芯片,两者都由

组成,合计16个SE。每个芯片具有128 CU/8192个流处理器,总计256 CU/16384个流处理器,辅以新的XGMI互联规划,且每个小芯片都具有VCN 2.6引擎/主IO控制器。

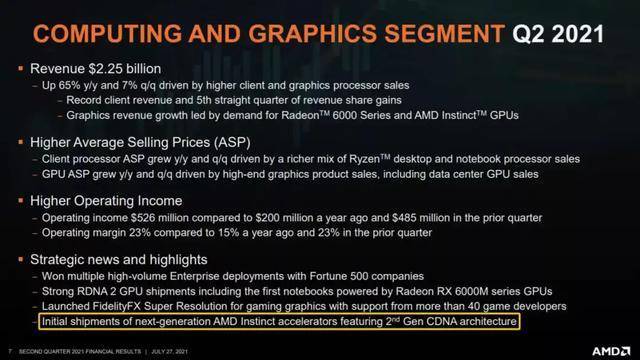

AMD CNDA 3(MI300)和英伟达Ampere的下下一代,都有望选用台积电的N3工艺节点。

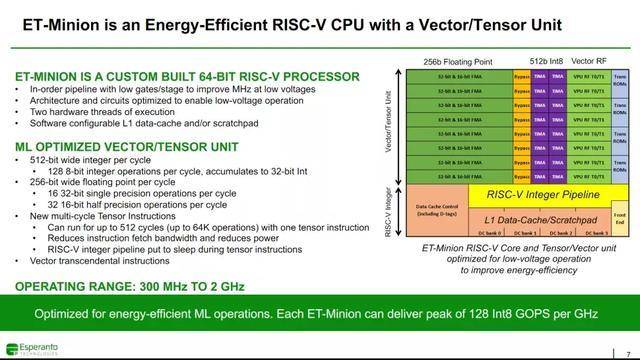

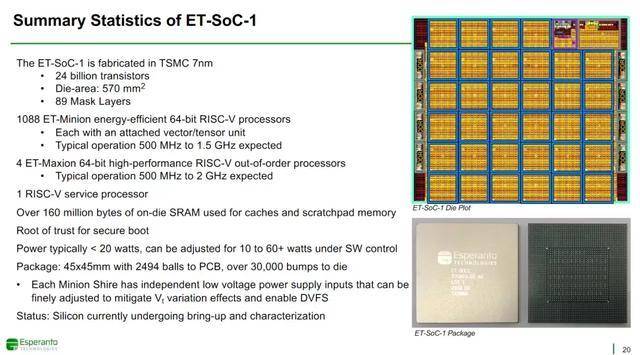

更小尺度、低功耗的ET-Minion 64位RISC-V内核,能够并行运转,轻松履行作业负载,期望成为最高功能的商用RISC-V芯片。

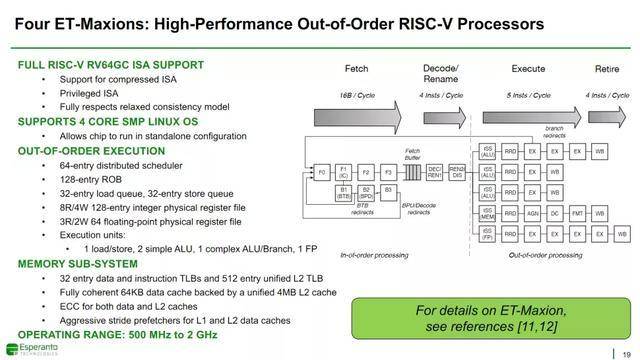

的功率运转,习惯体系功率约束。是一种通用的并行处理解决方案,能加快许多可并行化的作业负载。为了合作小内核,Esperanto封装了额定4个高功能ET-Maxion 64位RISC-V 内核。较小的内核是按次序履行规划,而较大的内核是为乱序履行规划的。

它支撑PCIe Gen4、256位宽(四通道)LPDDR4x内存,并具有用于安全发动、体系管理和计时器的 RISC-V 服务处理器。

渠道声明:该文观念仅代表作者自己,搜狐号系信息发布渠道,搜狐仅供给信息存储空间服务。

上一篇:股票行情快报:北方华创(002371)5月22日主力资金净卖出947292万元 下一篇:三星的工艺、封装路线图