公开课46期笔记 长电科技文声敏:从半导体开展史看未来封装集成三大趋势

时间: 2023-08-06 14:13:06 | 作者: 新闻动态

集微网音讯,集微直播间自开播以来获得了很多来自职业的重视与好评。其间“集微公开课”栏目联合职业头部企业,经过线上直播的方法共享精彩主题内容,一起建立直播间文字发问互动环节。集微网期望将“集微公开课”栏目打造成我国ICT工业最专业、优质的线上训练课程,深化产教交融,助力我国ICT工业开展。

集微网第四十六期“集微公开课”于7月21日(周三)上午10:00直播,邀请到长电科技规划服务工作中心总经理文声敏,带来以《从半导体开展的前史看封装的趋势》为主题的精彩讲演。

长电科技规划服务工作中心总经理文声敏以助听器的技能演变为例指出,半导体技能开展前史是协助人们日子体会不断晋级的进程。封装技能虽不像规划和制作环节开展迅猛,但也按着“一代芯片需求一代封装”的开展轨道稳步前行,特别跟着互联网和物联网的不断开展,封装技能开端朝着集成方向开展。而手机和消费电子运用关于无线化、小型化、集成化与功用化的开展需求,以及核算机趋于高功能CPU,都对封装技能提出了更苛刻要求。

跟着集成电路商场规划不断扩大,需求愈加多样化,封装技能和工业链又将产生怎样的改变?

文声敏表明,在2000年曾经,封装技能首要以焊线为主,这之后倒装得到很多运用。现在,先进封装技能如SiP开展迅速,但跟着封装体积越来越大,未来十年将需求新的技能来完结异构集成,并满意商场产品对功用、功能以及更快上市的需求。

不过文声敏指出,传统封装和先进封装技能有不同的运用场景,比方倒装芯片的功能要求高、集成度高、速度快,因而智能手机等终端运用选用的器材中,包括多种封装方式。短期内,传统封装和先进封装不会呈现“谁替代谁“的问题。

依据职业的研讨数据,到2023年,裸芯片引线键合(WB single die)封装占全体商场比例将降至60%,到达3050亿美元;SiP引线键合(WB SiP)封装商场比例将添加到12%;倒装封装(FlipChip)比例增至27%,2.5/3D、FOWLP/PLP等先进封装有望到达1.4%。

展望封装架构开展趋势,也有一些是曾经的架构运用新的技能,比方FO SiP(扇出型体系级封装)技能。相较PoP(叠层封装)技能,FO SiP封装可以使产片厚度减小40%,热阻下降40%,内存带宽添加400%等。

在前30年里 ,IC规划、封装规划与PCB板级集成分别由晶圆厂、封测厂及原始设备制作商厂各自完结。

文声敏以为,未来工业链三方协同规划是必然趋势。从封装厂视点来说,越早介入IC 规划阶段,整个进程本钱下降的越多,现在工业链正朝着这一方向开展。不过他指出,此趋势下应战包括来自EDA软件的多物理场模仿、多尺度跨过等问题,处理协同规划的应战需求三方有机联合。

此外,调查全体工业链,晶圆厂正活跃拓宽先进封装技能,估计将进一步加重商场竞争。

第三,未来封装将朝着定制化方向开展,这将对资料、设备,及工业链上下游协作提出更高要求。

跟着半导体制作工艺继续微缩,芯片规划的约束越来越大。传统的单个大芯片战略现已行不通, 使Chiplet概念应运而生。

文声敏指出,制作Chiplet子芯片最大的两个应战在于设备和资料。以设备为例,要制作子芯片,需求具有高牢靠和精细的设备,但设备出资将十分高。

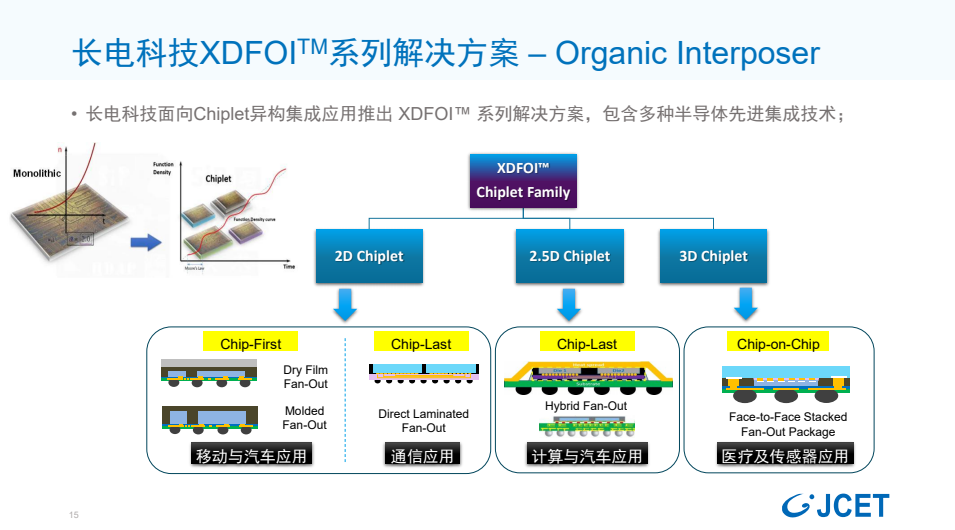

据了解,现在长电科技面向Chiplet异构集成运用推出了 XDFOI™ 系列处理计划,包括多种半导体先进集成技能。其间,2D Chiplet首要面向移动与轿车运用以及通讯运用;2.5DChiplet首要面向核算与轿车运用;3DChiplet适用于医疗与传感器运用。

半导体技能开展至今,异构集成等微体系集成计划已成为芯片工业的新方向,以“密布”和“互连”为根底特征的先进封测技能催生了一个新的概念——“芯片制品制作”。跟着芯片对功能等方面不断提出更高的要求,封装技能将在集成电路制品制作中发挥越来越重要的效果。

公开课65期笔记 场景化SoC OpenCPU计划怎么更好地在智能表计中运用?

上一篇:先进封装迎来用武之地长电科技推进“芯片制品制作”走向国际 下一篇:芯片封装或成半导体开展下一个竞技场