半导体制作之集成电路的制程工艺篇

时间: 2023-08-09 21:18:36 | 作者: 新闻动态

近来,Intel宣告暂缓晋级以色列一晶圆厂—前期方案耗资110亿美元,面向未来的10nm及7nm工艺工厂。这一决议或许是因为10nm和7nm工艺的商用尚存在瑕疵,也有或许是为了优先出资其在爱尔兰首要出产14nm级芯片的工厂,然后直接处理14nm产能缺乏的问题。

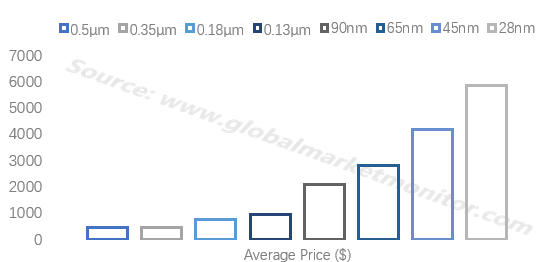

14nm或是10nm都是集成电路内部的间隔,间隔的长短表现了集成电路的精密度,而这种精密度取决于制程工艺。密度越高,功耗越小,功用越杂乱,价格也越高,高密布度是当时的趋势。

不同于概念,限于机器和人力的工业是有极限的。在抵达5nm这个公认的极限之前,制程工艺的开展已然放缓,摩尔定律逐渐失效。绝地,各个企业也面临着工艺与商用的开展难题,整个职业进入后摩尔年代。

因为领导职业进程开展需求承当昂扬的研制费用,在抵达制程工艺理论的极限之前,龙头企业现已连续撤离。格芯官方宣告放置7nm FinFET项目,将重心转移到14/12nm FinFET的衍出产品和其他差异化产品上。联电宣告抛弃12nm以下制程,而英特尔将战略改为“制作-架构-优化”,屡次推延10nm芯片量产冷清。

而在2017年头,台积电第一代7nm工艺成功制作256Mbit SRAM芯片,良率高达76%。不过,在7nm工艺节点上占有控制位置的绝地,台积电的研制费用不断增加,到达了其他企业的数倍之多。

而高额的科研投入也正是一流企业差异于追逐者的重要因素。台积电现在在IC制作职业占有肯定领先位置,营收也逐年攀升。

跟着摩尔定律逐渐失效,寻求更精密的IC需求投入的科研资金更加可观。为了获取更多赢利,一流企业在抢占产品先进制程的绝地,也依托本身品牌优势在旧节点商场抢占比例。更有甚者,比方台积电,乃至将事务向工业结尾的封测环节延伸。一流企业要坚持可持续开展,仍是应该使用制程工艺的先进水平,开发现已到达商用水平而二流企业没有霸占的节点。

28nm为现在单位逻辑闸本钱最小的技能节点,长周期制程特点显着,估计大多数产品将逐渐向更先进制程搬迁,达至28nm后因其更高性价比以及广泛的应用领域将逗留较长冷清。二线nm后,已足以满意绝大多数半导体产品的制程需求,应该掌握现有制程商场,并推出特征工艺渠道来提高竞争力。

上一篇:半导体封装工艺流程图(芯片封装) 下一篇:一文详解晶圆制作规划流程